Accueil > Technique > Digital > Présentation des trames de commande DCC

Présentation des trames de commande DCC

Présentation des trames de commande DCC

mercredi 12 mai 2021, par ,

Présentation des trames de commande DCC

Nous avons vu dans un article précédent Introduction aux commandes DCC que le système DCC envoyait un signal contenant des informations qui circulaient dans les rails.

Par convention le rail droit dans le sens de la marche est au potentiel 18 v, le rail gauche est à 0 v. Le signal émis par la centrale est rectangulaire et oscille entre -18 et + 18 v pour avoir la puissance de traction des rames et accessoires. Cette tension est beaucoup trop élevée pour les composants électroniques d’un décodeur. La première chose qu’il fera c’est d’abaisser cette tension à + 5v et redresser le signal pour ne garder que les alternances positives.

Après ces opérations électroniques, on obtient un front haut de 0 v à 5 v et un front bas de 5 v à 0 v.

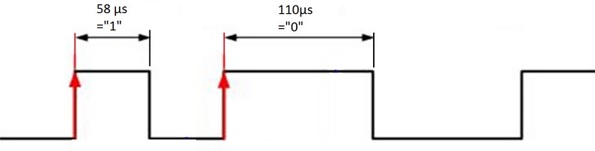

Ce signal véhicule de l’information en modulant sa fréquence, comme un code-barre ou un QRCode qui nous sont familiers le font mais de façon statique. C’est la durée des fronts hauts à +5v qui sont analysés. Par convention une durée de 58 µs code un bit à 1 et une durée de 110 µs code un bit à 0.

Exemple de trame vue à l’oscilloscope.

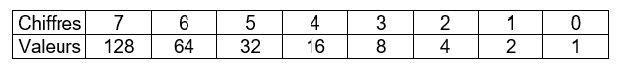

Si vous avez déjà oublié le contenu de l’article Bits octets et autres une toute petite piqure de rappel

Un octet permet de compter de 0 à 255. Voir le tableau ci-dessous

Pour convertir un nombre binaire en valeur décimale il suffit d’additionner les valeurs de chaque bit à 1 dans l’octet par exemple :

00000000 = 0

00000001 = 1

10000010 =128+2 soit 130

10101000 =128+32+8 soit 168

11111111 = 128+64+32+16+8+4+2+1 soit 255

Donc la centrale envoie régulièrement des paquets d’instructions sur la voie, par exemple avec le protocole XpressNet (Lenz) la centrale est responsable de la génération des paquets de suivi DCC, du maintien de la file d’attente prioritaire des paquets et du maintien de l’état général de l’ensemble du système, en particulier les fenêtres de transmission permettant d’envoyer une demande ou une instruction spécifique sans collision avec un autre paquet. Elle communique avec une fréquence de 62,5 kilobits par seconde.

Une trame DCC est constituée comme suit :

– Un préambule d’au moins 10 bits à 1 pour signaler aux décodeurs qu’ils vont recevoir un ordre.

– Un bit à 0 (Start) pour signaler le début de transmission,

– Un ou deux octets d’adresse séparés par un bit à 0,

– Un bit à 0 comme séparateur

– Un ou deux octets de commande séparés par un bit à 0,

– Un bit à 0 comme séparateur

– Un octet de contrôle (E) permettant de vérifier s’il n’y a pas eu de problème de transmission. Le contrôle utilise l’algèbre de Boole en effectuant un OU EXCLUSIF sur les octets 1 ( A) et 2 (B) voir Quand 1+1 fait 1

– Un bit à 1 pour signaler la fin de transmission (Stop)

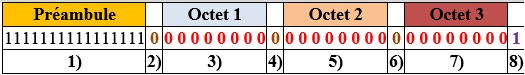

Trame DCC minimum :

A pour adresse, D pour la donnée transmise et E pour le contrôle.

1111111111 0 AAAAAAAA 0 DDDDDDDD 0 EEEEEEEE 1

Trames de commande de locomotives

Limitons-nous dans un premier temps à l’analyse du protocole DCC utilisé pour la commande des locomotives. On se référera aux fiches 670 et 671 du MOROP (Union Européenne des Modélistes Ferroviaires et Amis des Chemins de Fer) Normes - NEM - MOROP et celles du NMRA Microsoft Word - S-9.2.1 2012.07.doc (nmra.org) et pour les adresses étendues.

Il y a 4 trames différentes en fonction de la programmation du décodeur. Ce qui importe c’est de savoir si l’adresse est courte Cv 1 ou longue Cv 17 et CV 18 ET du nombre de pas de vitesse Cv 29.

La trame comportera :

– 3 octets pour une adresse courte et 14 ou 28 crans de vitesse.

– 4 octets pour une adresse longue et 14 ou 28 crans de vitesse.

– 4 octets pour une adresse courte et 128 crans de vitesse.

– 5 octets pour une adresse longue et 128 crans de vitesse.

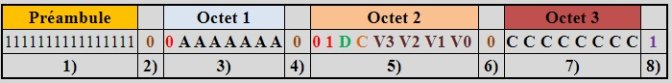

Voyons plus finement la structure d’un message sur trois octets, un octet de données d’adresse A, un octet de données d’instructions D, C, Vet un octet de contrôle C. Ce message sera compris par une locomotive dont l’adresse est courte (jusqu’à 99 pour Lenz et 127 pour les autres) et dont la courbe de vitesse est programmée en 14 ou 28 pas.

1) Il y a d’abord un préambule d’au moins 10 bits à 1 (préférable 12), pour annoncer la trame.

2) Puis un bit START de démarrage de paquet à 0.

3) Puis un premier octet contenant l’adresse. Le bit 7 est à 0 pour annoncer l’adresse en binaire sur 7 bits puisque les adresses courtes sont codées jusqu’à 128. Les 7 bits suivants A6, A5, A4, A3, A2, A1 et A0, codent l’adresse en binaire.

4) Un bit de START à 0.

5) Le deuxième octet contient une commande ou des données. Ici le bit 7 est à 0 et le bit 6 à 1 pour indiquer un codage de vitesse sur 14 ou 28 pas. Le bit 5 (D) indique le sens de marche (1 marche avant, 0 marche arrière). Le bit 4 (C) est à 0 pour une marche 14 pas et à 1 pour le 28. Les bits suivants représentés par V3, V2, V1, V0 codent la vitesse, d’après le tableau ci-dessous pour une marche à 28 pas.

6) A nouveau un bit de séparation START à 0.

7) L’octet 3 est un octet de contrôle. Dans la transmission de la trame, il peut toujours y avoir de parasites dues au mauvais contacts roues/voie par exemple qui détériorent le message. Ce contrôle sert de clé pour tester la bonne réception du contenu des octets 1 et 2. C’est un calcul de XOR (OU EXCLUSIF) effectué par la centrale. C’est de l’algèbre binaire pour ceux que cela intéresse. Le décodeur fait le calcul de son côté et le compare avec celui envoyé dans la trame par la centrale. S’il y a divergence, le paquet est rejette.

8) Le message se termine par un bit à 1.

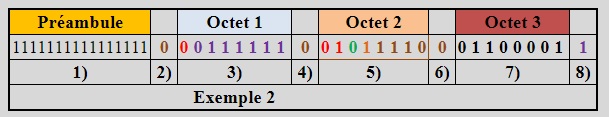

Un exemple

Voici le message envoyé à la locomotive dont l’adresse est 63 (octet 1 adresse 01111111= 0+32+16+8+4+2+1=63), qui roule en marche avant (bit 5 de l’octet 2 à 1), au pas 26 (bits 0, 1, 2 et 3 de l’octet 2 respectivement à 0, 1, 1, 1 voir tableau), sur une marche à 28 pas de vitesse (bit 4 de l’octet 2 à 1).

Le décodeur quand il reçoit ce message doit

- 1°/ Valider le préambule.

- 2°/ Remplir bit par bit les octets consécutifs, ici il y en a 3 mais il peut y en avoir 5 comme on l’a vu plus haut.

- 3°/ Détecter le bit de fin de trame (bit zéro après le dernier octet)

- 4°/ Vérifier que la structure de la trame correspond à la trame souhaitée (accessoire/loco/prog...). Calculer le bit de contrôle et le comparer à celui émis par la centrale. Si tout est Ok, le système électronique exécute l’ordre.

- 5°/ Transmettre les informations reçues au décodeur.

- 6°/ Effacer les Octets[i] et invalider le préambule pour être prêt à recevoir une nouvelle trame.

Un exemple sur 5 octets, c’est-à-dire une machine avec une adresse longue et 128 pas de vitesse.

1) Il y a d’abord le préambule d’au moins 10 bits à 1 (14 bits sont préférables) pour annoncer la trame

2) Puis un bit de START à 0.

3) Le premier octet contenant le début de l’adresse. Elle est codée sur 14 bits donc nécessitant 2 octets. Les bit 7 et 6 sont à 1 pour annoncer l’adresse longue. Et les 6 bits suivants codent l’adresse en binaire (A13, A12, A11, A10, A9, A8), avec les bits du second octet.

4) Un bit de séparation à 0.

5) Le deuxième octet contient la suite de l’adresse sur 8 bits, (A7, A6. A5, A4, A3, A2, A1, A0), le premier bit est l’adresse de poids fort :

6) Un bit de séparation à 0.

7) Le troisième octet commence par le bit 7 à 0, le bit 6 à 0 et le bit 5 à 1 pour indiquer que l’octet suivant le quatrième est entièrement dédié à la vitesse. Les 5 bits suivant à 1 codent le 128 pas de vitesse.

8) A nouveau un bit de séparation à 0.

9) Le quatrième octet contient une commande ou des données. Ici le bit 7 (D) est une donnée indiquant le sens de marche (0 marche arrière, 1 marche avant). Les bits suivants représentés par (V6, V5, V4, V3, V2, V1, V0) codent en binaire le pas de vitesse, poids fort en tête. S’ils sont tous à 0 c’est un ordre d’arrêt d’urgence avec inertie, tous à 1 stop arrêt d’urgence immédiat. Je n’ai pas dessiné le tableau de 128 lignes qui codent les pas de vitesse, la progression suit la même logique que celui établi plus haut pour une marche à 28 pas de vitesse.

10) Un bit de séparation à 0.

11) L’octet 5 est l’octet de contrôle qui calcule le contenu des octets 1, 2 , 3 et 4.

12) Et pour terminer le bit de STOP à 1.

Trames particulières

Trame de remplissage ou trame IDLE

Sur trois octets, après le préambule, tous les bits de l’octet 1 sont à 1 et ceux de l’octet 2 à 0. En recevant ce paquet TOUS les décodeurs ignorent les instructions qui suivent, elle sert à maintenir la puissance sur le réseau.

Trame de reset du décodeur.

Sur trois octets, après le préambule, tous les bits sont à 0 dans les octets 1 et 2. A la réception de cette trame TOUS les décodeurs effacent leur mémoire volatile (vitesse, direction), et arrêt des locomotives. Tous les bits de l’octet 1 sont à zéro, cet octet code l’adresse c’est pourquoi l’adresse 0 est interdite.

Trame de STOP.

L’octet 2 qui code la vitesse, le sens de marche et le pas de vitesse contient des instructions permettant de désactiver l’arrivée du courant moteur. La locomotive stop faute d’énergie.

Le bit 0 (S) à 0 le décodeur doit entamer une procédure d’arrêt en tenant compte des consignes de décélération, si le bit est à 1arrêt immédiat par coupure de courant d’alimentation

Voilà. Dans un autre article on détaillera les trames pour décodeurs de fonctions et les trames de décodeurs d’accessoires.

Merci à Centrale DCC version 2 et dcc

Enfin voyez les article de Dominique sur Locoduino comme par exemple. LOCODUINO - L’Arduino et le système de commande numérique DCC

Si vous voulez voir les trames en transformant votre PC en oscillo Espion DCC – Centre DCC, un utilitaire mis au point par Mr Ferrari le créateur de Centre DCC et aussi Analyseur de Trame DCC (pagesperso-orange.fr).

Vous trouverez aussi une très bonne vidéo de Noel Danjou qui a développé un programme de décryptage des trames sur

Trains Essonne Nord

Trains Essonne Nord